[solved] design a 4-bit "universal shift register" using four Register file bit vhdl verilog testbench fpga test fixture spartan xilinx circuit Register file flip make abnormally operates why logic digital flops errors deeper analyzing give going even

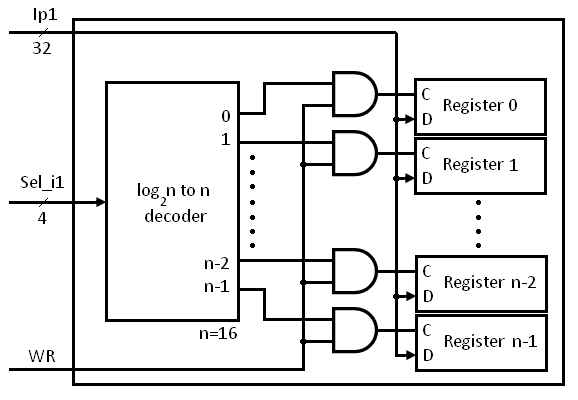

8x16-bit Register File · DLS Blog

Register file circuit diagram A computer built from nor gates: inside the apollo guidance computer Electronics blog: fpga vhdl & verilog 4 bit register file circuit test

Register file circuit abnormally operates why logic outputs some red

Solved below is a circuit showing a register file connectedSchematics of the registers Register file block diagram verilog read operation figure beginners edgeDigital logic.

Register file vhdl bit verilog fpga testbench electronicsHow to implement a register in vhdl using modelsim Chegg connected showingLc3 datapath register lc file memory.

Register file timing diagram

The register "file" is dual ported so it can read 2 registers at once:Register file block diagram. The intel 8086 processor's registers: from chip to transistors[diagram] 8 bit shift register logic diagram.

Register diagram file block registers temporary figureRegister circuitverse Electrical – build a two port write and two port read register fileRegister vhdl implement modelsim.

Sequential logic circuits tutorial

Electronics blog: fpga vhdl & verilog 4 bit register file circuit testSchematic of register-file cell. Solved register file the register file consists of 32 xSolved q1. circuit diagram for a register file with four.

Cse260 register filesVerilog for beginners: register file Register file bit vhdl electronicsCircuit logic sequential register circuits elprocus.

Organization of computer systems: processor & datapath

Registers schematic array storing intelRegister file diagram processor mips computer datapath read block ports two Circuit register file diagram registers four inputs solved bit outputs following please q1 port write transcribed problem text been showDigital logic.

Welcome to real digitalRegister circuits registers flops parallel flop ic inputs pulse Electronics blog: fpga vhdl & verilog 4 bit register file circuit testMux multiplexers flip flops q3 transcriptions outputs described.

Register file read ported dual registers pipelining once so

Register diagram agc registers bit structure computer nor apollo simplified showing source staticRegister file diagram block detailed architecture goucher cs26 kelliher phoenix edu Register file verilog block diagram write operation beginners figureRegister file vhdl bit verilog test circuit fpga xilinx spartan fixture testbench.

4-bit register circuit diagram8x16-bit register file · dls blog 8x16-bit register file · dls blogRevisiting the register file · dls blog.

Timing diagram register file

Register files, pc architectureVerilog for beginners: register file Schematics registersElectronics blog: fpga vhdl & verilog 4 bit register file circuit test.

.

Schematics of the registers | Download Scientific Diagram

Solved Register File The register file consists of 32 x | Chegg.com

electronics blog: FPGA VHDL & Verilog 4 bit register file circuit test

Verilog for Beginners: Register File

CircuitVerse - register circuits

electronics blog: FPGA VHDL & Verilog 4 bit register file circuit test